※この記事はASCII.jpからの転載です(文中リンクはASCII.jpの記事に飛ぶことがあります)

Zero Bubbleで分岐予測精度を向上

Branch Predictorには新たにZero Bubble Branch Predictionを採用したとする。実はAMDは2013年に“Bandwidth increase in branch prediction unit and level 1 instruction cache”という特許を取得している。

この特許では分岐予測の処理の中で“One Bubble”(No-Operationな1命令)を追加することで、BP(Branch Prediction)とHP(Hash Prediction)の両方をうまく動かせ、結果として分岐予測精度が上がるというものである。

察するに今回のZero Bubbleは、このBubbleを0、つまりNo-Operationな命令を追加せずに、例えばTagのような形でBubbleがいることを示す形で効率化を図った、というあたりに読めなくもない。

ただ実は“Zero Bubble”に関してはSamsungが“High performance zero bubble conditional branch prediction using micro branch target buffer”という特許をすでに取得済であり、これとの関係が気になるところである。

このあたりは、もう少し深い話をAMDが説明してくれるまで筆者としてもお手上げである。ただ結果として冒頭の画像のように、これでIPCが1~2%程度は改善しているようなのでバカにはできない。

Load/Storeユニットの帯域を倍増

Load/Storeに関しては、例えばAGUもひょっとすると4つになっている可能性を否定できないが、それよりもLSU(Load/Store Unit)の帯域を倍にする方が効果的だろう。実際、FPUを強化するというからには、1サイクルあたりで処理できるデータ量が増えることになる。

Zen 2のLSU周りは連載516回で示した通り、読み込み64Bytes/サイクルと書き込み32Bytes/サイクルを同時に行なえる構成になっているが、これを倍増しているのではないかと考えている。

連載516回で説明したZen 2のLoad/Storeユニット

ちなみにこのZen 3の世代ではまだAVX512をサポートするという話はない(Zen 4世代というのがもっぱらの噂である)が、FPUを増やすことでAVX256命令の処理能力を倍にするなら、LSUも相応に強化する必要がある。そしてこれはALUの処理性能向上にもつながることになる。

キャッシュのプリフェッチについては、正直よくわからない。あるいは3次キャッシュの容量が実質倍になったことに向けて、アルゴリズムや実装を強化したのかもしれない。

さて、ここまでコアの内部を強化すると、当然コアのエリアサイズが増える。それにもかかわらず、ダイサイズがほぼ変わらないように見える。

ダイサイズがほぼ変わらないように見える。この写真が本当にZen 3世代のものか? というとそれはそれではっきりしないのだが……

後述するように3次キャッシュのトータルサイズは変わらない。ここで効いてくるのが、冒頭で書いた「N7→N7+ではトランジスタ密度が1.2倍になる」という話である。今回、プロセスの変更で増えたトランジスタは、すべてコアの改良につぎ込んだのではないかと思う。

おそくCCDダイの原価そのものはほとんど変わらないであろう。なぜなら、ArF→EUVでマスクコストは減るが、EUVを利用することによるコストアップで相殺されるからだ。このあたりの話は連載581回で説明している。それでもIPCの向上につながるのなら、これは大きなメリットであろう。

ついに8コアになったCCXと

容量が2倍になった3次キャッシュ

次にCCX(Core Complex)周りについて。Zen 3世代では、ついにCCXが8コアに変更になった。連載496回で筆者がZen 2の推定される構造の1つとして紹介した構成がやっと実現した形だ。

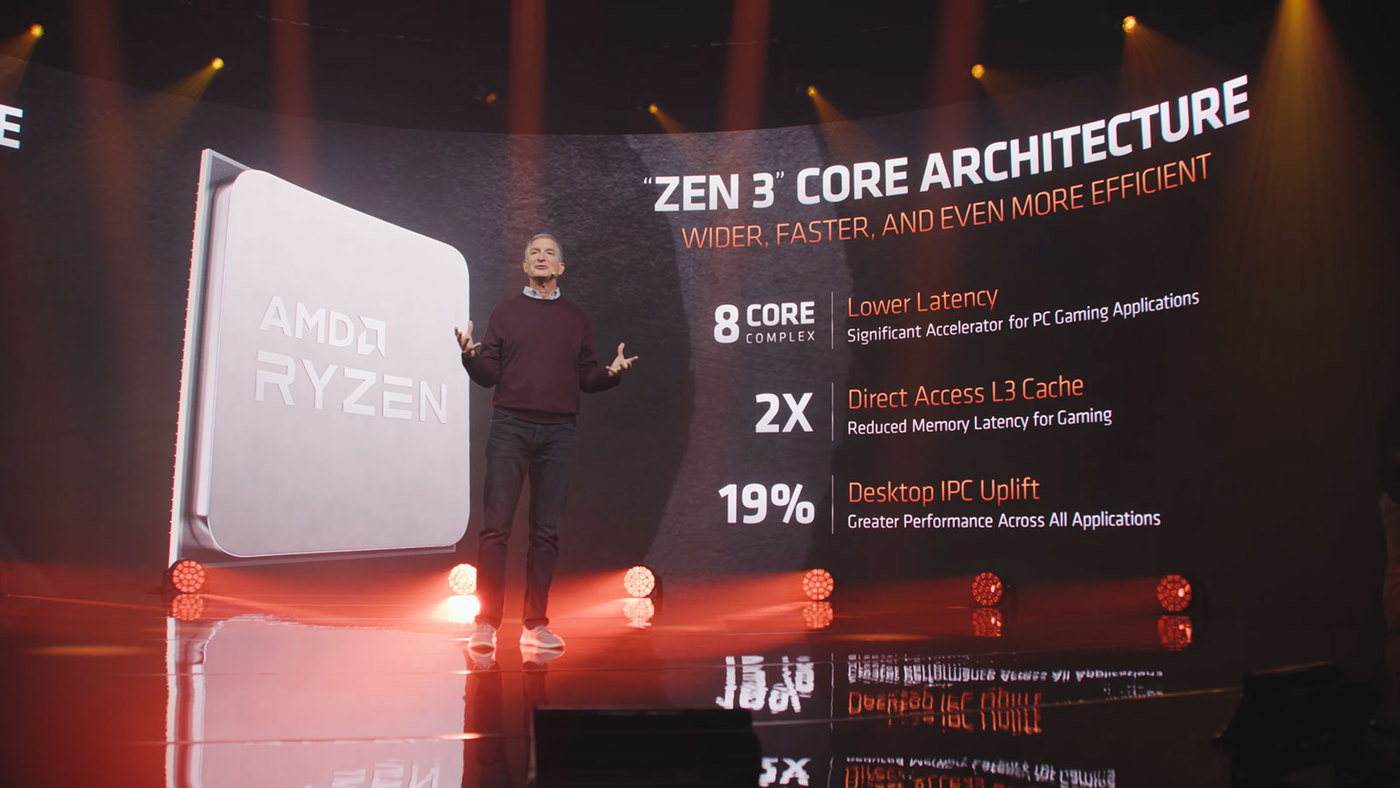

Zen 3世代ではCCXが8コアになった。この2Xは容量が2倍の意味になる

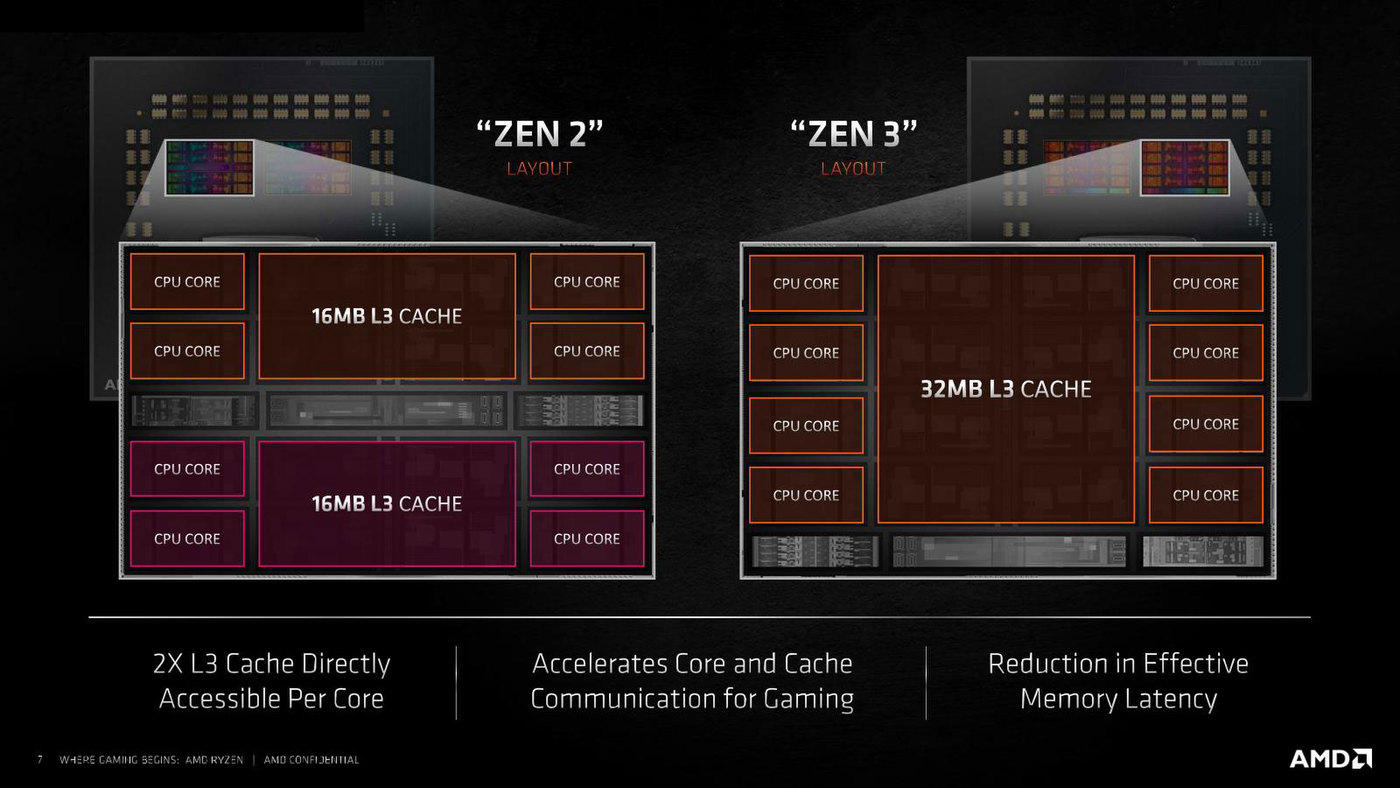

下の画像が内部構造であるが、やっとすっきりした形だ。

Zen 3の内部構造。8コアのRyzen 7 5800Xまではレイテンシーが非常に低く抑えられることになり、性能向上につながるだろう

実際Zen 2までは、2つのCCXの間の通信は、一度CIoD(I/O Die)経由で行なうことになっており、32MBの3次キャッシュと言いつつも、実質的な3次キャッシュの容量は16MBに限られていた。

ところがZen 3ではこれが32MBになり、またコア間の通信も同一CCX内になるので、ずっと高速化(低レイテンシー化)された。もちろんこれはCCD(Core Complex Die)が1つの場合の話で、2つ以上では引き続きCIoD経由での通信になるので、その場合のレイテンシーは大きくなる。

ちなみにそのCIoDの話であるが、Ryzen 5000シリーズに採用されるCIoDは、Ryzen 3000シリーズのものと完全に同一である。Zen 3の世代で、AMDの開発チームはCCDの改良に全力を注いでおり、CIoDに関してはそのままとされた形だ。

もっともCIoDに手を入れる必要があるか? といえば、実はあまりない。メモリーに関してはDDR4-3200まで定格でサポートし、オーバークロック動作でもDDR4-4200+は比較的容易などと以前説明があったほどなので、改良の余地は少ない。

PCI ExpressもすでにGen 4に対応しており、まだGen 5は対応製品も存在しないので、やはりやるべきことはあまりない。

これがZen 4の世代になると、DDR5メモリーとPCI Express Gen5の対応が必要になり、マザーボードも当然変更になる(DIMMのスロットそのものが変更になる)から、当然CIoDも作り直しになる。であれば、Zen 3の世代は特にCIoDをいじらずに先送りにしよう、という発想は理に適っている。

それもあってか、今回チップセットに関しては特に言及がなかった。今のところAMD 600シリーズチップセットに関しては発表がない。世代的に言えばUSB 4.0をサポートしたAMD 600シリーズが投入されても不思議ではないのだが、これは後送りになるようだ。

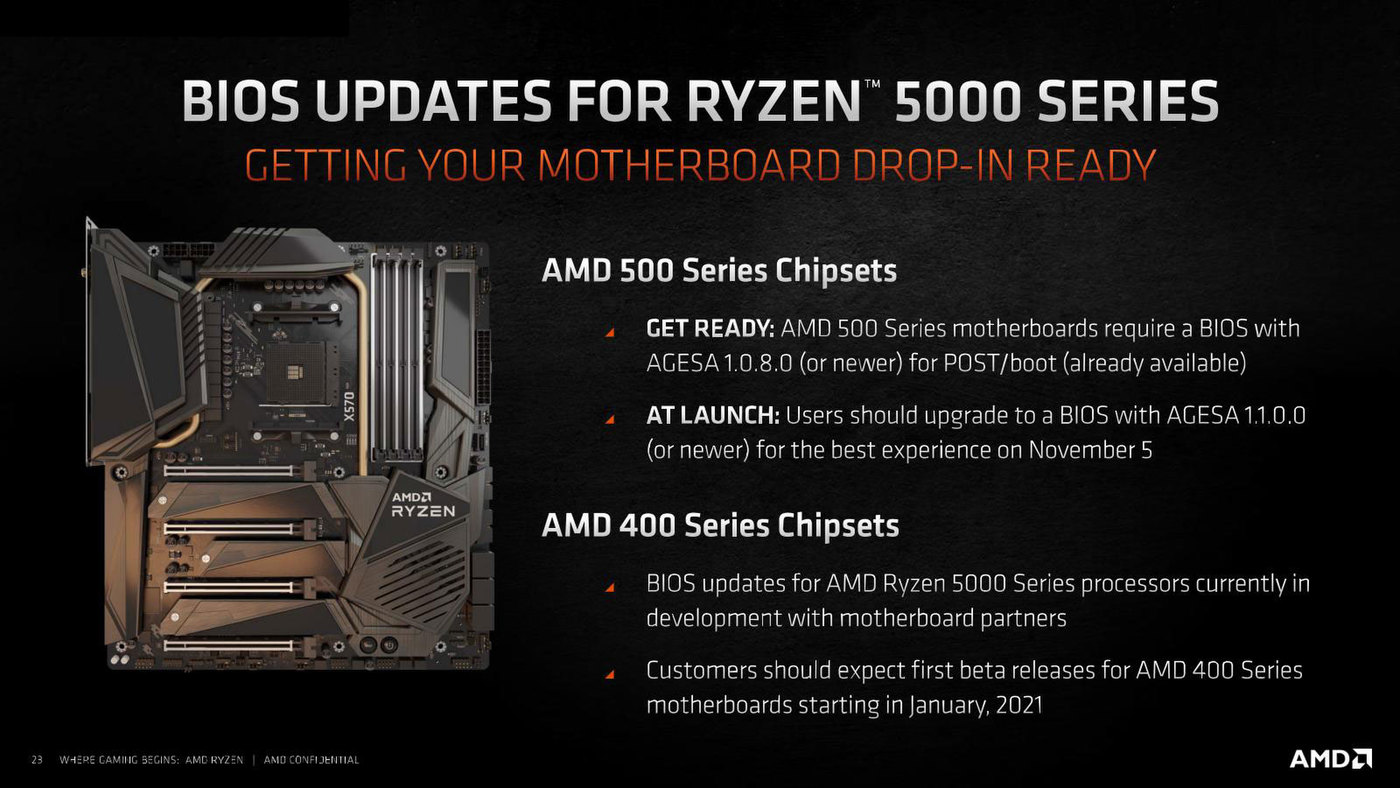

したがって当面はAMD 500シリーズと、AMD 400シリーズが対応するチップセットということになる。ただし発売時にサポートされるのはAMD 500シリーズのみで、AMD 400シリーズのサポートは2021年1月を予定しているという話であった。

とりあえず動くだけなら、AMD 500シリーズ+AGESA 1.0.8.0対応BIOSで可能だが、フルパフォーマンスを発揮するにはAGESA 1.1.0.0対応BIOSが必要とのこと。KTU氏がベンチマークをスタートするまでに、提供されるだろうか?