※この記事はASCII.jpからの転載です(文中リンクはASCII.jpの記事に飛ぶことがあります)

Ryzen 5000シリーズで押さえておくべきこと

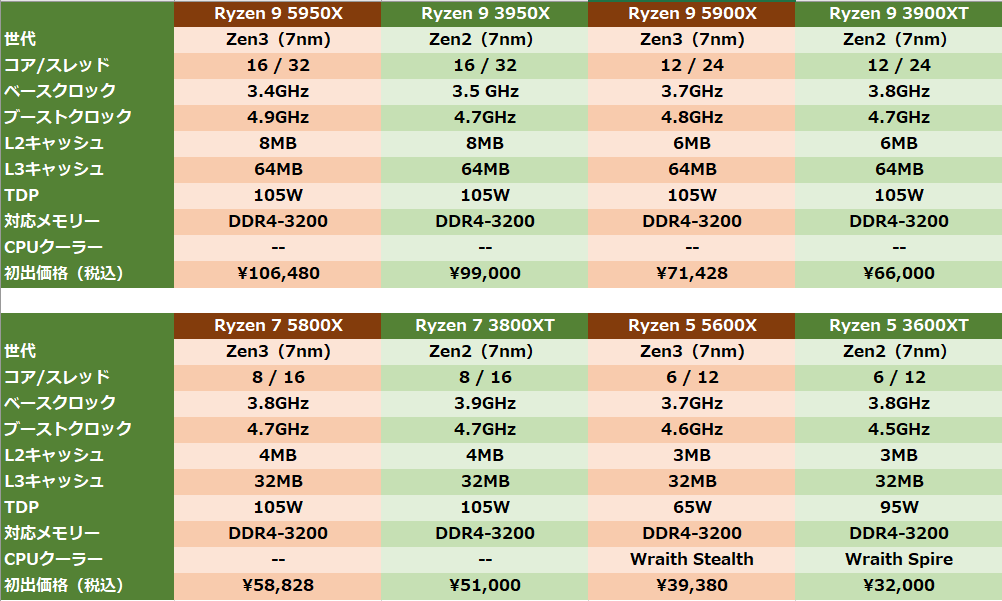

ベンチマークの前にRyzen 5000シリーズを知る上で押さえておくべきポイントをいくつか挙げておこう。まずはスペックのおさらいから始めよう。

Ryzen 5000シリーズと、その近傍の製品とのスペック比較。価格は全て初出価格で比較している

●ポイント1:プロセスルールに変更はない

AMDは製品の製造プロセスにおいて業界トップを独走している。10nmを中々モノにできないインテルや、先日8nmプロセスを採用したGPUをリリースしたNVIDIAよりも微細な7nmプロセスを採用している(このルールに厳密な比較基準があるかは別の話)。

AMDはZen2ベースのRyzen 3000シリーズにおいて初の7nmプロセスを採用した経緯から、Zen3ベースのRyzen 5000シリーズでは、さらにそれを改善したプロセスが採用されるのではないか……と噂されていたが、AMDはメディア向けのブリーフィングにおいて明確にそれを否定した。

AMD曰く“7nmプロセスのレシピ”を改善することでクロックを引き上げることに成功し、それを使って今年7月のRyzen 3000XTシリーズを製造、そのレシピはRyzen 5000シリーズでも使っている、とのことだ。プロセスルールにおいて独走状態の今、プロセス変更の労力は次世代のZen4に集中させ、Zen3は完成度の向上に主眼を置いた、ということなのだろう。

さらに、11月18日より販売開始とされる同社の次世代GPU「Radeon RX 6000」シリーズでもローンチイベントにて“同じ7nmプロセス”という表現をした。つまりAMDとTSMCはCPUとGPUで7nmプロセスの技術蓄積をふんだんに行ない、その結果Radeon RX 6000シリーズの価格設定をライバルより大幅に安くすることに成功したのではないだろうか。

●ポイント2:ダイはCCX×2から単一CCXになり、レイテンシー大幅減

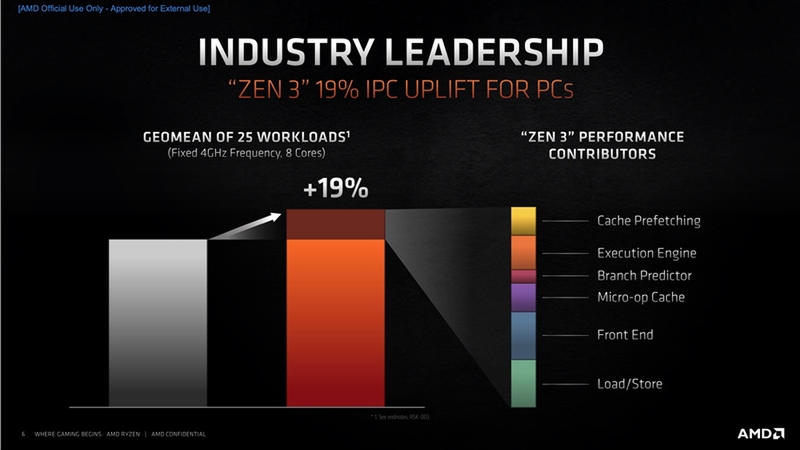

Ryzen 5000シリーズはプロセスが据え置きなぶんIPC(Instructions Per Second)の向上に注力した。AMD曰くIPC上昇幅は前世代の+19%増とのことだが、この増分はCPUのあらゆる側面を少しずつ伸ばした結果である、と謳っている。

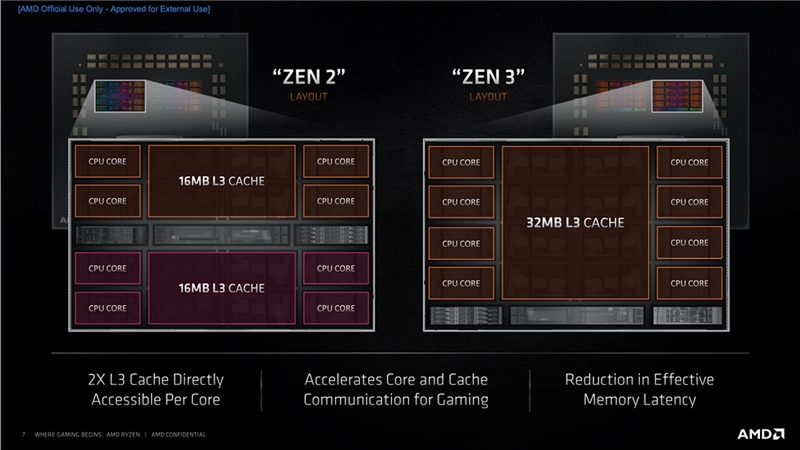

だがその中でも特筆すべき点はCCD(Core Chiplet Die)の構成が従来のCCX(Core Complex)を2基連結したものから、単一のCCXに変更されたことだ。1ダイに8コアを載せたCCDがあった場合、従来は4コア+4コアの構成だったが、Ryzen 5000シリーズでは8コア1基に統合されている。この変更により、あるコアからアクセス可能なL3キャッシュの量が2倍になり、コア⇔L3キャッシュのレイテンシーが大幅に削減されることになる。

RyzenのL3キャッシュは基本的にL2から追い出されたデータを置くビクティムキャッシュなので、コアからアクセス可能なL3キャッシュが倍増するということは、パフォーマンス向上に大いに寄与することができる。

今回もCPUデザインはCCD+IOD構成であるため、CCDを2基搭載するRyzen 9 5900Xおよび5950Xよりも、CCDが1基しかないRyzen 5 5600XとRyzen 7 5800Xの方がレイテンシーを小さくできるという違いはあるが、コアレイアウトの変更により、2CCDでもよりレイテンシーが短くできることになる。

AMDの資料より抜粋。Zen3のIPCはZen2と同コア&同クロックとした場合平均19%増加したが、これはCPUのあらゆる側面を少しずつ伸ばした結果であると謳っている

Zen2の8コアCCDはCCXを2基連結している関係上、L3が16MBずつに分断されていたが、Zen3の8コアは単一CCX構成。各コアからアクセス可能なL3キャッシュの領域が倍増し、レイテンシー削減に大きく寄与した。ゲーム用途にはこの変化が一番嬉しいだろう

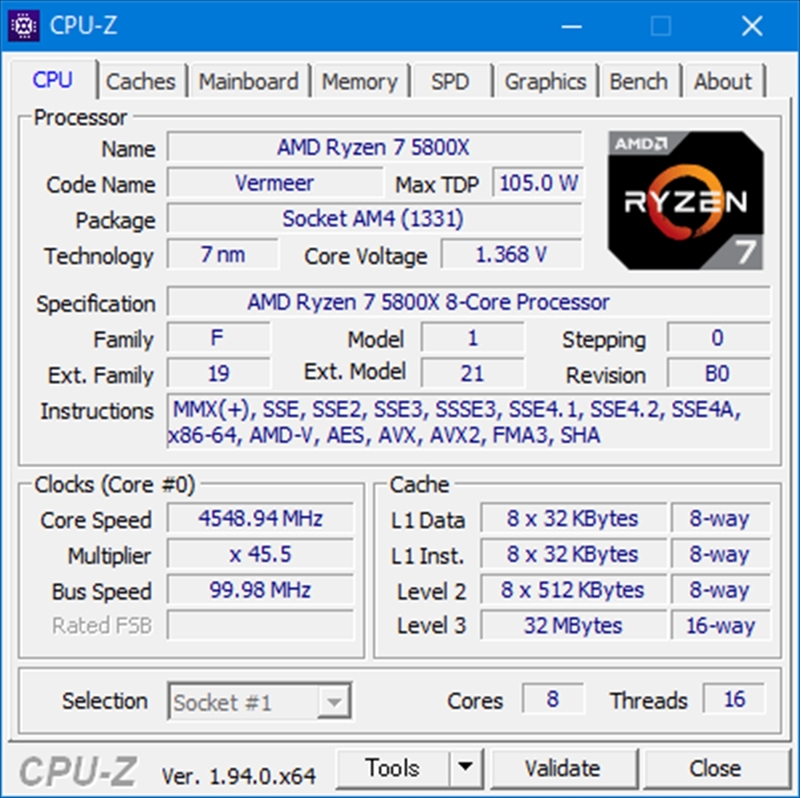

「Ryzen 7 5800X」の情報を「CPU-Z」で拾ってみた。8コア(C)16スレッド(T)のCCDが1基あるだけなので、L3キャッシュは32MBがひとかたまりであることが示されている

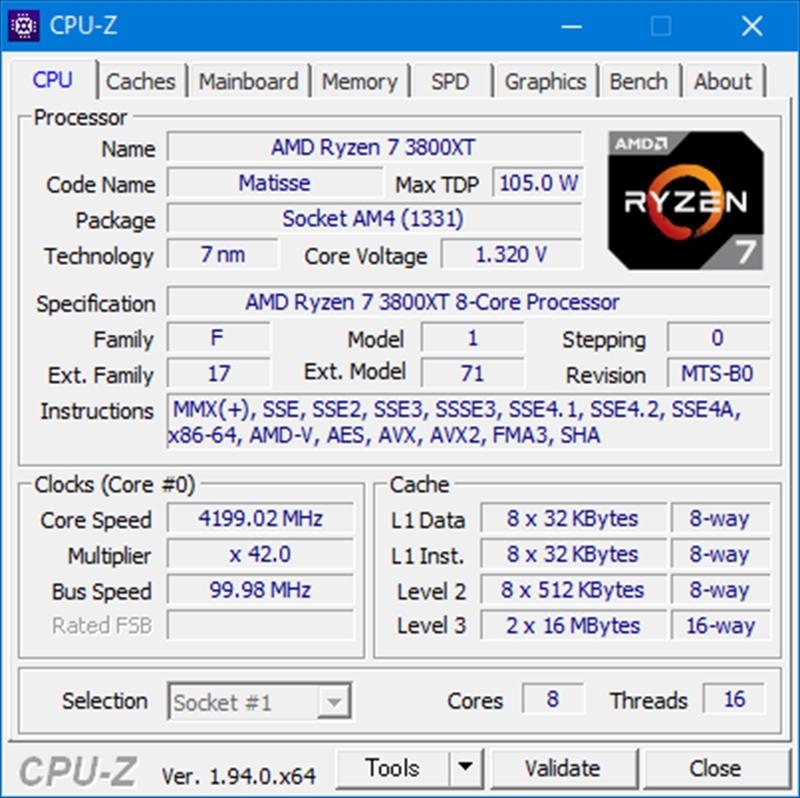

1世代前の「Ryzen 7 3800XT」では、L3キャッシュは16MB×2構成

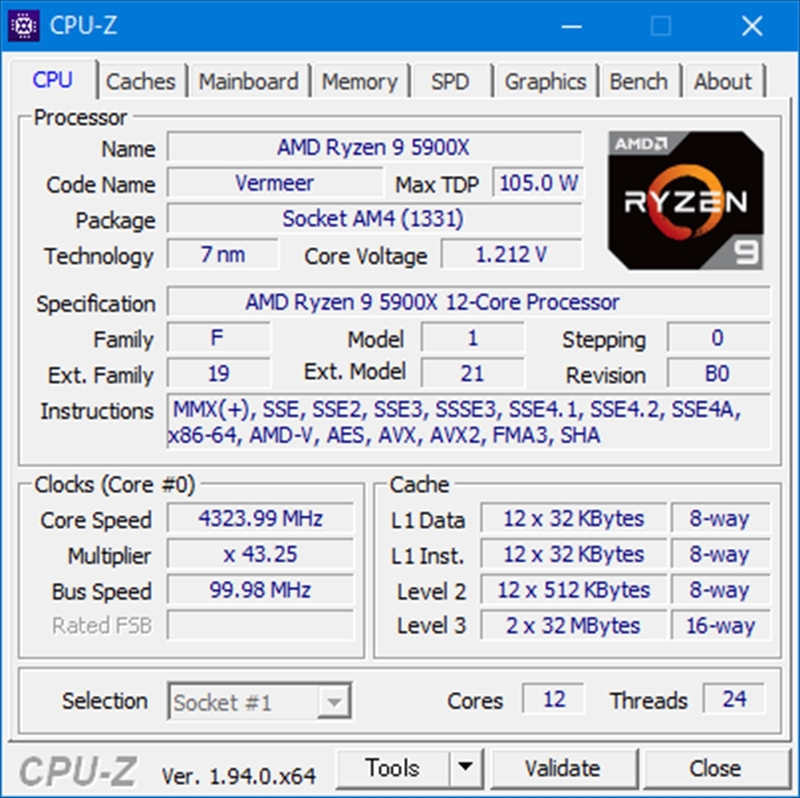

「Ryzen 9 5900X」では6C12TのCCDが2基実装されているので、L3キャッシュも32MB×2構成となる

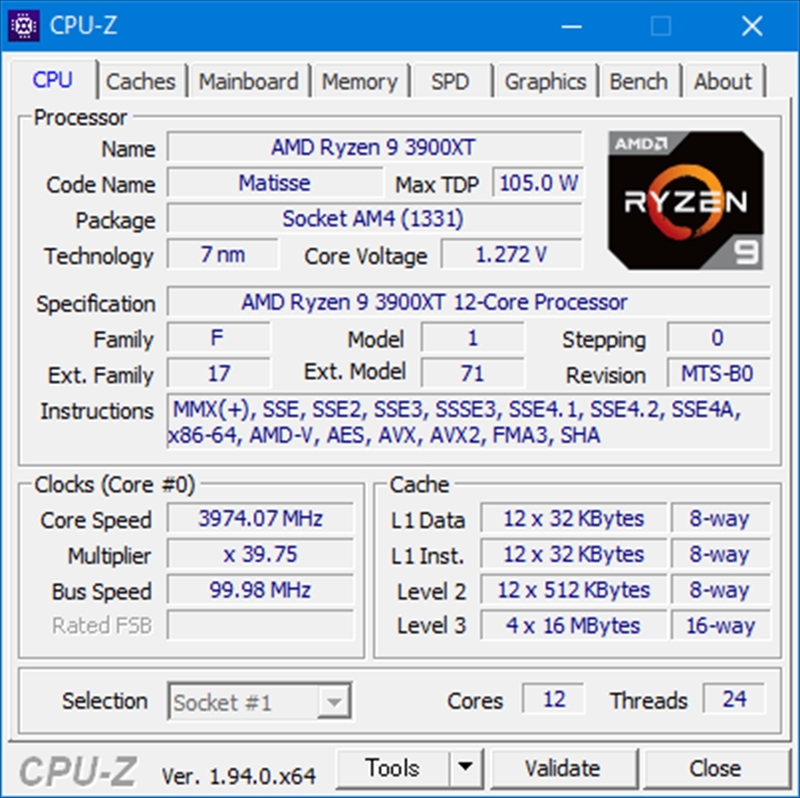

Ryzen 9 3900XTも6C12TのCCD×2だが、各CCDには2基のCCXが入っているのでL3キャッシュは16MBのブロックが4つという表現になる

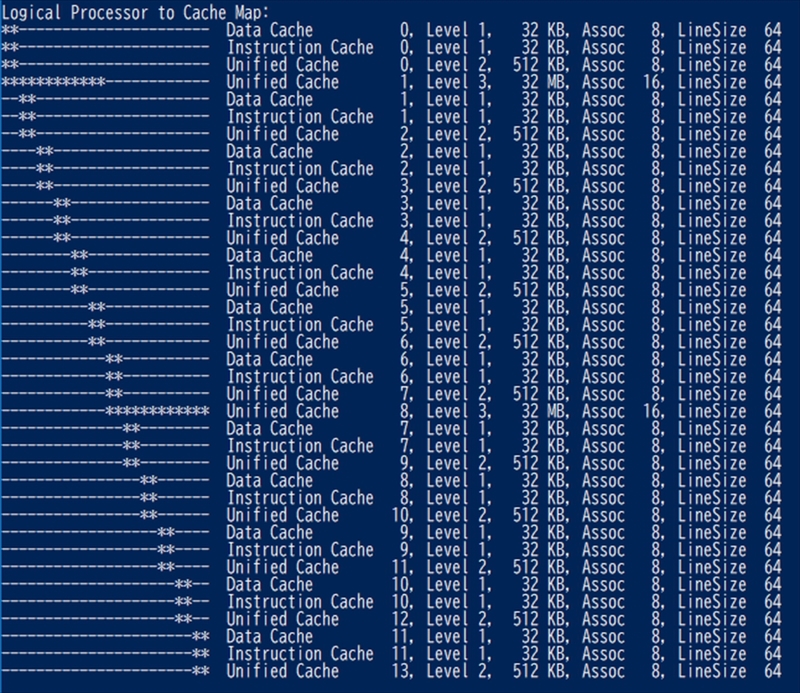

「CoreInfo」でRyzen 9 5900Xのコア/キャッシュ階層を確認。L3キャッシュが2つあり、それぞれに論理コア数にして12基が接続されている