※この記事はASCII.jpからの転載です(文中リンクはASCII.jpの記事に飛ぶことがあります)

3D V-Cacheによる積層で

キャッシュ容量を大幅に増量できる

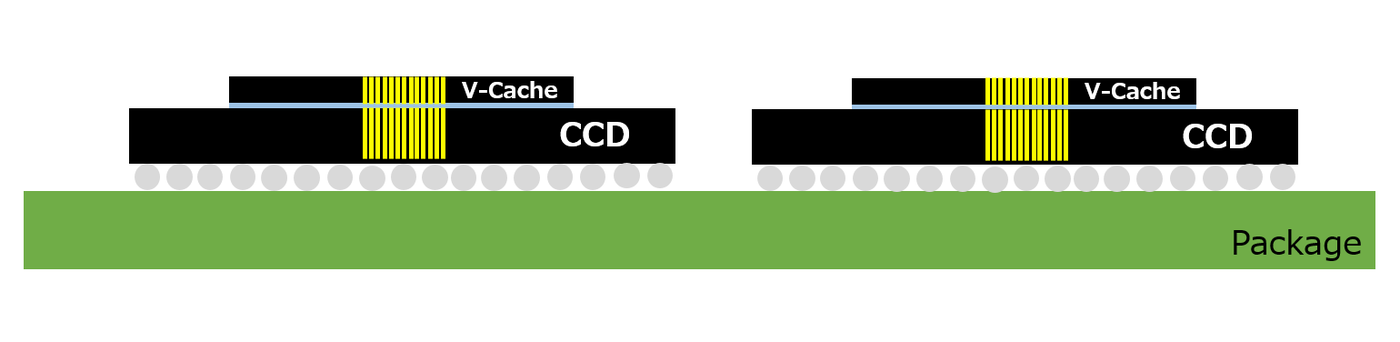

だいぶ3次元積層技術の話が長くなってしまったが、話を3D V-Cacheに戻す。今回はRyzen 9 5900Xを利用したプロトタイプなので、構造は下図のようになる。2つのCCDの上に、64MBのV-Cacheが載り、これも3次キャッシュ(以下、L3)として利用できるので、プログラムから見るとL3が96MBに増えたように見える構造だ。

3D V-Cacheの構造

実は基調講演終了後に、このV-Cacheに関してTwitterで多数のメンションが飛びまくった。中にいくつか「AMDからの返答をもらった」というものがあったので、筆者も直接「こういうメンションがTwitterで飛んでいるが事実か?」をAMDの広報に確認をして返事をいただいている。それによって以下のことが公式に確認された。

V-Cacheの構成は1層。容量は64MB。

V-Cache構成とすることの、放熱に関する影響は軽微である。他の3次元積層の方式と比較しても圧倒的に優れており、従来の2Dシリコンそのままとほとんど差がない。

V-Cacheのレイテンシーは、CCD上のL3アクセスよりもわずかに増える。ただ一般論としてキャッシュサイズが増えればどうしてもレイテンシーは大きくなり、これはV-Cacheも例外ではない。ただ、64MBのL3増加にともなうDRAMアクセス頻度の低下を考えれば、V-Cacheのレイテンシー増加は問題にならない程度と考えられる。

V-Cacheの消費電力は大きな影響はない。

CCDはV-Cacheを積む関係で、薄型化されている。

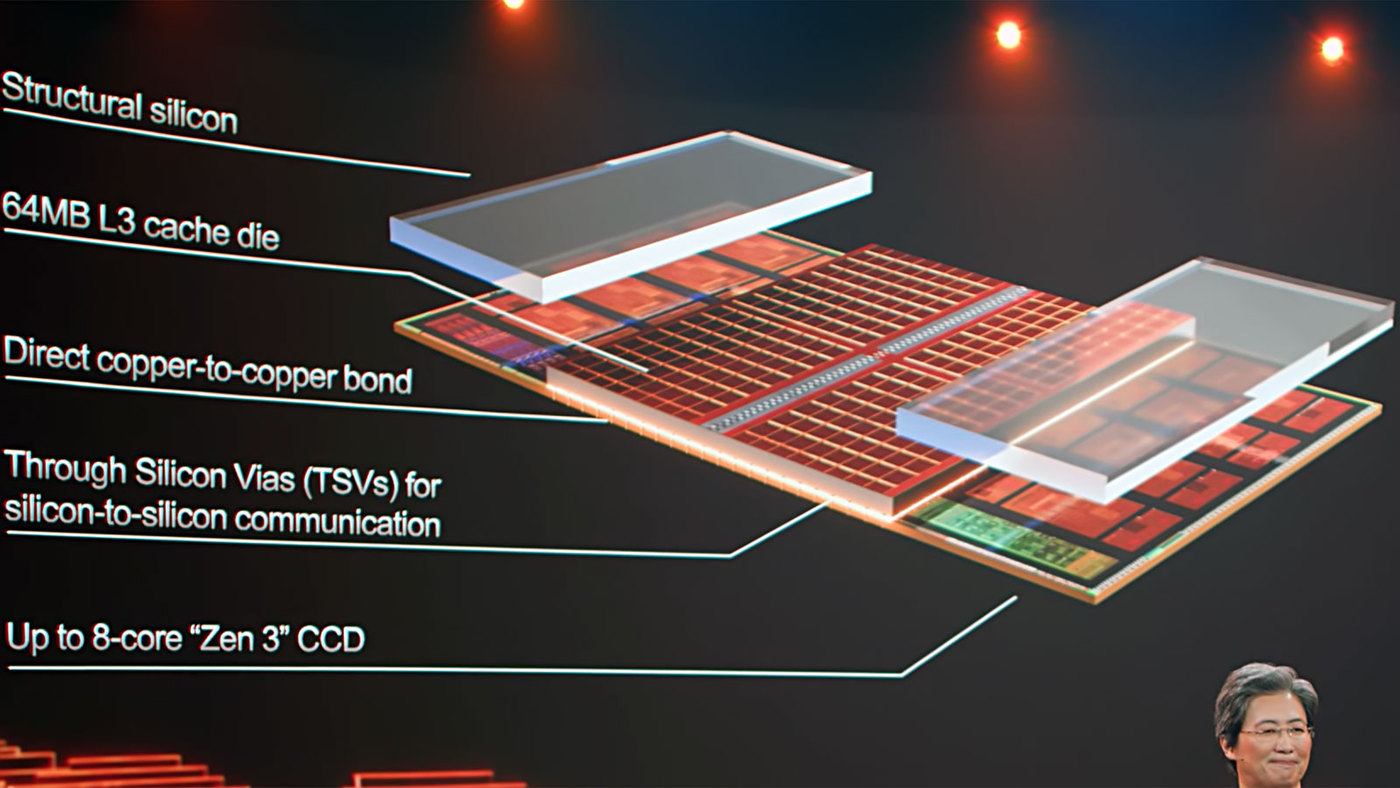

これをベースにもう少し構成を解説しよう。まず容量の件。下の画像は基調講演における構造図であるが、“64MB L3 cache die”はどう見てももともとのCCDの半分程度の面積しかない。

基調講演の36分17秒頃の映像の上を抜き出したもの

実際Su CEO自ら「6×6mmのSRAMをCCDの上に載せている」と明言しており、フットプリントは36mm2ということになる。この数字は丸めていると思うので、多少誤差はあるだろう。Zen 3のダイサイズはおおむね80mm2とされるから、ざっくり半分といったところだ。

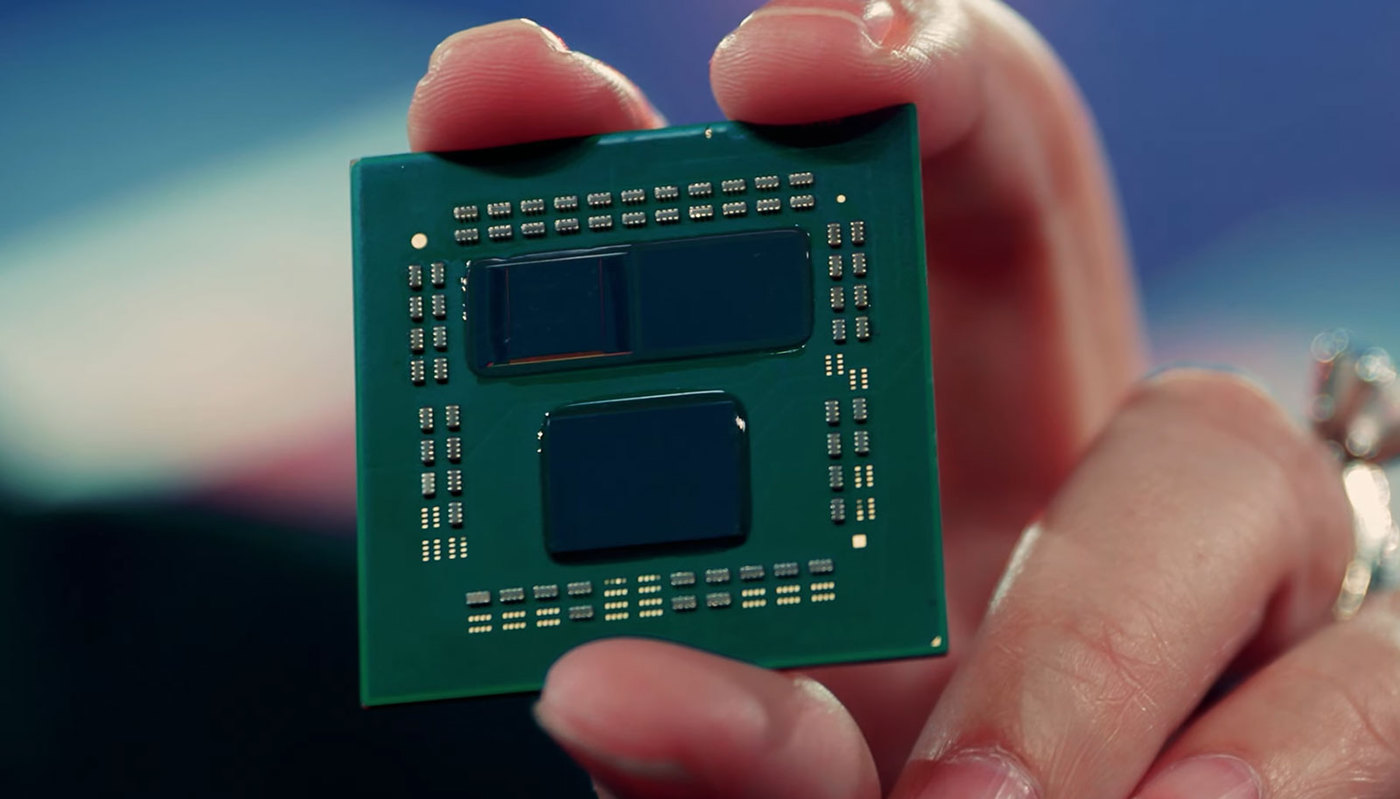

基調講演の35分59秒付近。左側のダイで、色が変わっている部分がV-CaceのL3とみられる

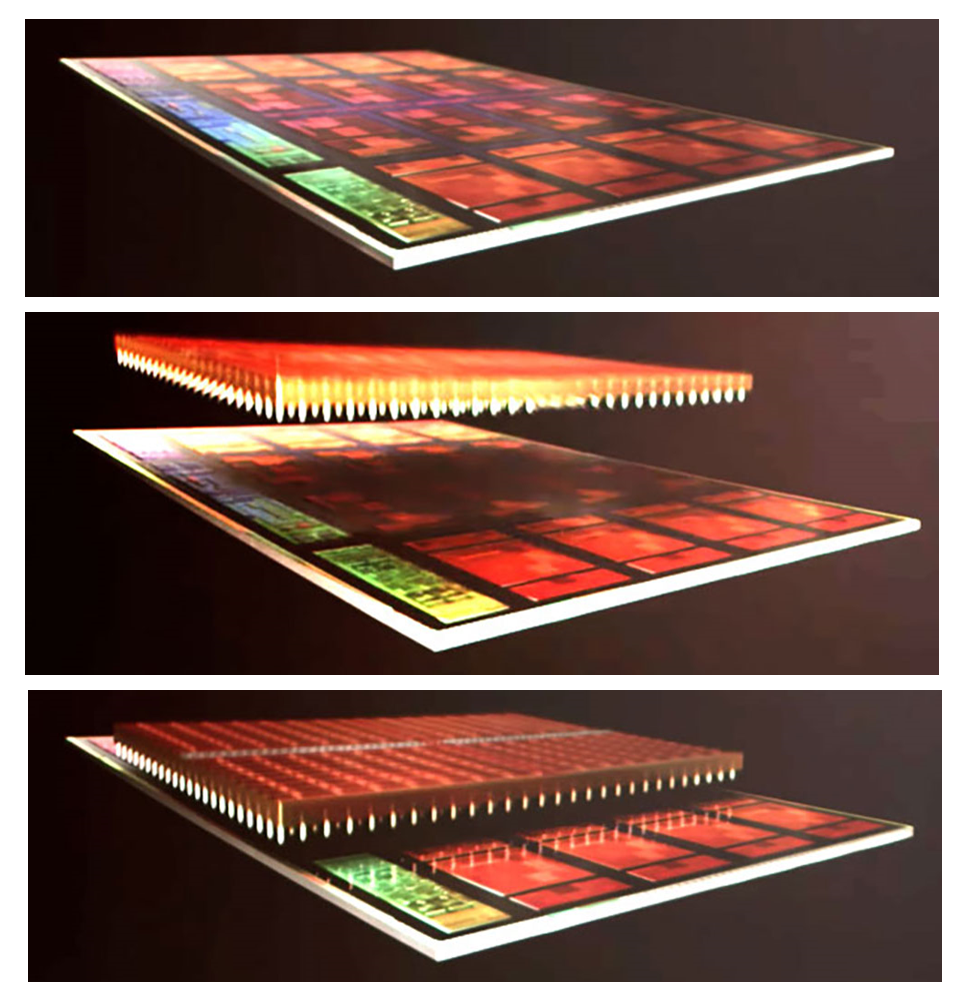

さて、Zen 3のCCDそのものも、もともと半分くらいの面積をL3に充てていた(下の画像上段)。V-Cacheは、横幅に関してはほぼCCDのL3と同程度で、ただし縦方向はL3+Zen 3コアをはみ出して、インフィニティーファブリックのI/F部あたりまではみ出しているようになっている(下の画像中段)。

Zen 3のCCD

ちなみにこの画像ではV-Cacheの全面にTSVが出ているように描画されているが、これは単なる映像効果であって、実際にはこんなに出ていないだろう(上の画像下段)。

問題は「どうやって36mm2に64MB SRAMを押し込めるか」である。CCDのダイ上のL3面積は、画像からもわかるようにおおむね36mm2で32MB SRAMしか構成できない。そもそもSRAMは一番面積を喰うロジック回路であって、MLC NANDフラッシュのように1つのSRAMセルで2bitを記憶する方法がない以上、倍密度にする方法はなかった。

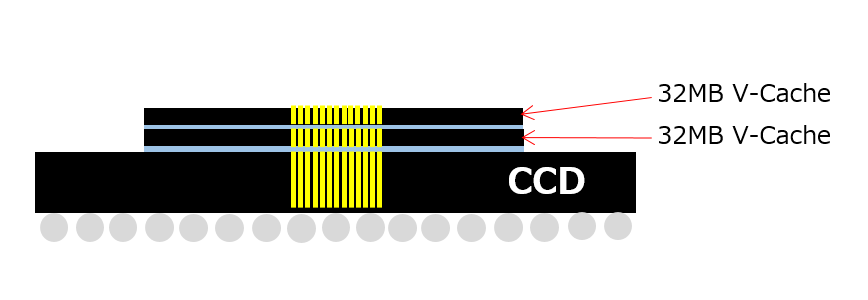

ではこれをどう解決したか?であるが、下図のように32MBのチップを2枚重ねればいい。そしてこの2枚重ねたものを「1層の64MB V-Cache」とAMDは言い張っているのだと思われる。そもそもSoIC自体、3枚以上のチップを積み重ねることを想定しており、こうした構成は難しくないと思われる。

32MBのチップを2枚重ねて、「1層の64MB V-Cache」としているのだろう

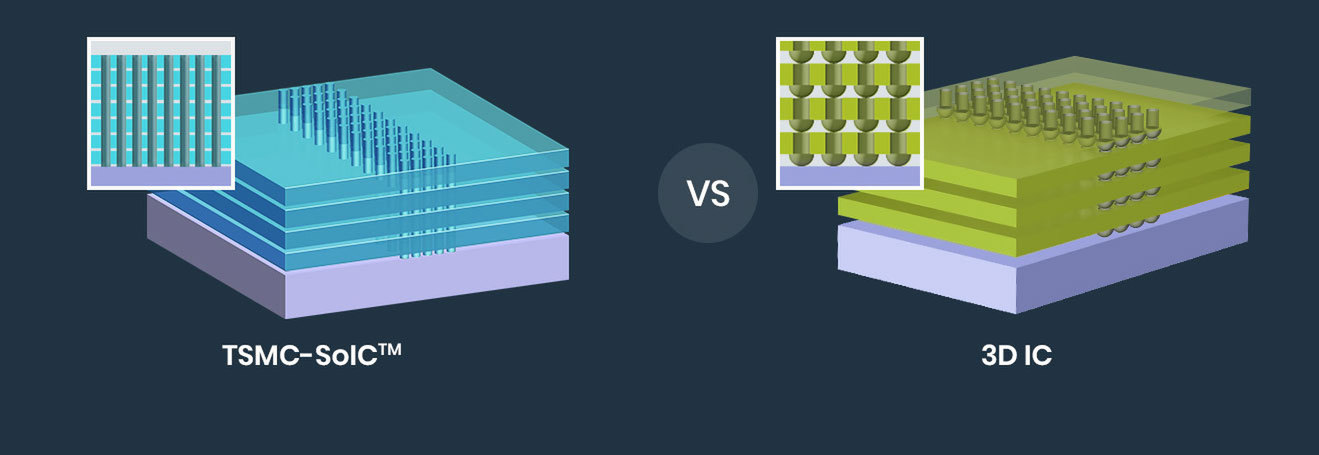

TSMCの“The Whats, Whys, and Hows of TSMC-SoIC”というページに掲載されたインフォグラムから抜粋。ベースとなるチップの上に4枚のロジックチップが積層されているのがわかる

実はこれ、傍証もある。Andreas Schilling氏の6月1日のメンションによれば、AMDのDaytona Platform(第2世代EPYC向けのサーバー向けプラットフォーム)にMilan(第3世代EPYC)対応BIOSをインストールすると、BIOS セットアップにX3Dという項目が出現し、最大4スタックまでの構成が選べるようになるそうだ。

Its always good to have a Daytona platform server at hand 😉 https://t.co/wdbCzsHMNH pic.twitter.com/JHjocLN6jP

— Andreas Schilling 🇺🇦 (@aschilling) June 1, 2021

氏のツイートが本当であるとすれば(これは今のところ確証はない)おろらくこれがV-Cacheで、32MBが1スタック、64MBが2スタック、128MBが4スタックになると思われる。