※この記事はASCII.jpからの転載です(文中リンクはASCII.jpの記事に飛ぶことがあります)

RDNA 3では2つのCUを1つにまとめ

CUの規模が4倍に増加

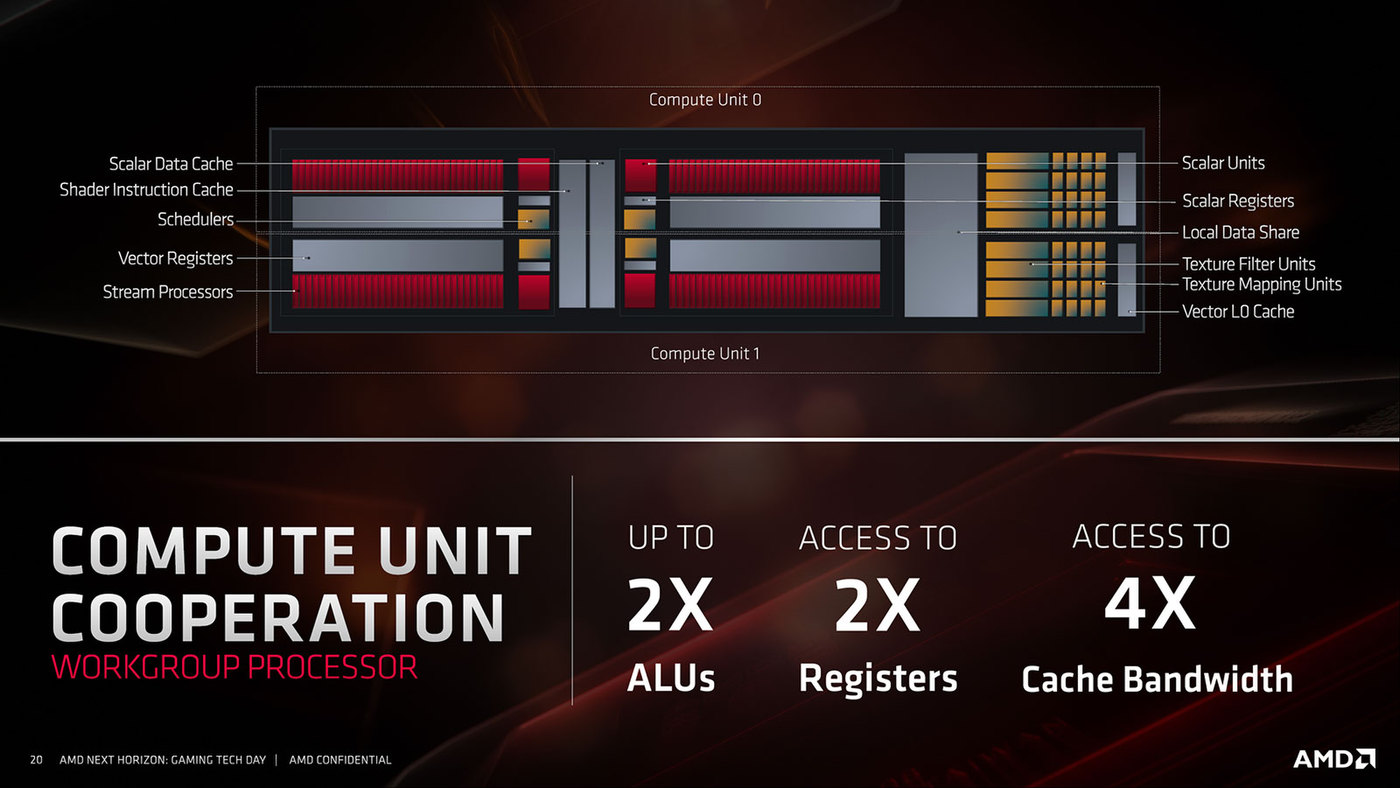

RDNAはCUを2つ束ねたものを、WGP(Workgroup Processor)として扱っている。このWGP、RDNA/RDNA 2の時点では、ハードウェア的には1つの管理単位であったが、ソフトウェアから見れば2つのCUとして見える形で、少なくとも明示的にWGPレベルでなにか管理、という話ではなかったはずだ。

RDNAはCUを2つ束ねたものをWGPとして扱っている。当初からWGPで管理すればよかったのに、と思わなくもない

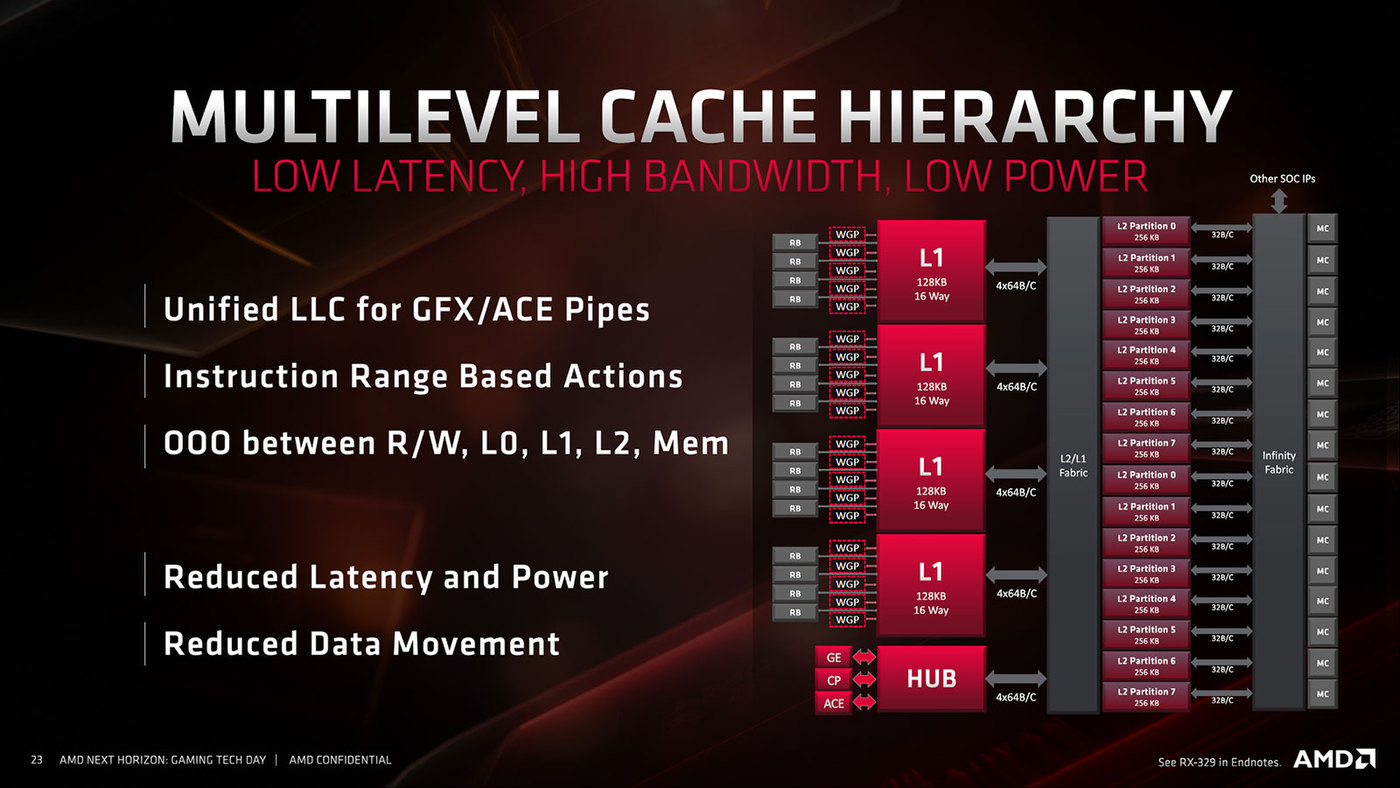

WGPには共有のローカルデータシェアやスケジューラー・データキャッシュ/スケジューラー・インストラクションキャッシュが配されていたが、5つのWGPで共有される形で128KB L1が配され、さらにその外側の外側にすべてのWGPで共有される形で4MB(256KB×16)のL2が配される形になっている。

このL2の容量はSKU(CU/WGPの数)によって変化する。RDNA 2では、このL2のさらに右側、インフィニティー・ファブリックにインフィニティー・キャッシュがL3として追加実装されているが、ここまでの基本構造は同じと考えていいだろう。

L1の総容量は当然WGPの数で変化するし、L2/L3もこれに合わせて変化すると思われる

ということで、ここでCUが廃されるというのはどういうことかと言えば、スケジューラーやベクトルキャッシュが、2つのCUで共通になるように構成された形で、しかもSP数が倍増するという構成になったと考えられる。

これはRDNAの図を基にした、RDNA 3のWGPの想像図。実際にはベクトル・レジスターの容量も倍増していそうだし、そもそもテクスチャーフィルター/マッピングユニットの数が1WGPあたり8/32個かどうかも疑問が残るところではあるが、想像図なので勘弁してほしい

要するにCUの規模が4倍になった形で、Wave 32を1サイクルあたり8つハンドリングできることになる。これをCUとして表現しなかったのは単に過去のCUとごっちゃになるのを避けたかったためだろうし、なぜ2CUを1つにまとめたかと言えば、おそらく規模を大きくするにあたり、より大きな単位で管理するようにすることでオーバーヘッドを減らしたかったのだろう。

ひょっとすると、Wave32に代わりWave64が管理単位として復活するかもしれないが、それなら32-Wide SIMD×8よりも64-Wide SIMD×4の方が合理的な気がするので、Wave32はそのまま継承されるだろう。

この、SP数が倍増したWGPが5つと、RB(Render Backend)がまとめて1つのL1を共有する、という構造そのものはRDNA 3でも変わらないようだが、RDNA 3ではこのWGP×5+RB+L1をまとめてシェーダー・アレイと呼び、これが最小単位になるらしい。つまり1280SP構成だ。