※この記事はASCII.jpからの転載です(文中リンクはASCII.jpの記事に飛ぶことがあります)

6月2日に配信されたCOMPUTEX 2021におけるAMDの基調講演はすでに加藤勝明氏の記事が上がっているのでごらんになった方が多いだろう。実はほとんどの内容は事前説明会で紹介があり、その意味では驚きはなかったのだが、最後に出てきた3D V-Cacheはその事前説明会でも一切触れられてこなかった話なだけに、正直仰天した。

COMPUTEX 2021で基調講演するLisa Su CEO

もっともこのところのAMDは、それこそ“One more thing”で本当にトンデモないネタが出てくるので、何か出てくると予想すべきではあったのだろうが、まさかこんなネタが! ということで、大いに驚かされた。ただ基調講演での説明は本当に最小限であり、技術的な話はあまり触れられてこなかったので、これを補足して説明していきたい。

TSMCの第3世代積層技術3D V-Cacheを採用したプロセッサーを

2021年末に量産開始

まず3D V-Cacheであるが、これはTSMCのSoIC(System on Integrated Chips)という技術を利用したものである。このSoICというのは、TSMCの第3世代積層技術として開発されてきたもので、2019年のSymposium on VLSI Technologyという学会で技術的な概略も発表されている。

ただSymposium on VLSI Technologyの場合は量産にまでたどり着かない、実験室レベルの研究もしばしば混じっているので、この時点ではこれが量産製品に適用されるかどうか疑問視されていた部分はあった。

ところが2020年11月にNIKKEI Asiaが「TSMCのSoICは、GoogleとAMDが最初の顧客となり、2022年に量産に入る」と報じており、この報道の真偽を含めて動向に興味が集まっていた。

今回の発表でこれが量産に耐える技術であり、しかも報道がほぼ正しい(Su CEOはV-Cacheを2021年末に量産開始すると明言した)ことが確認できたわけだ。

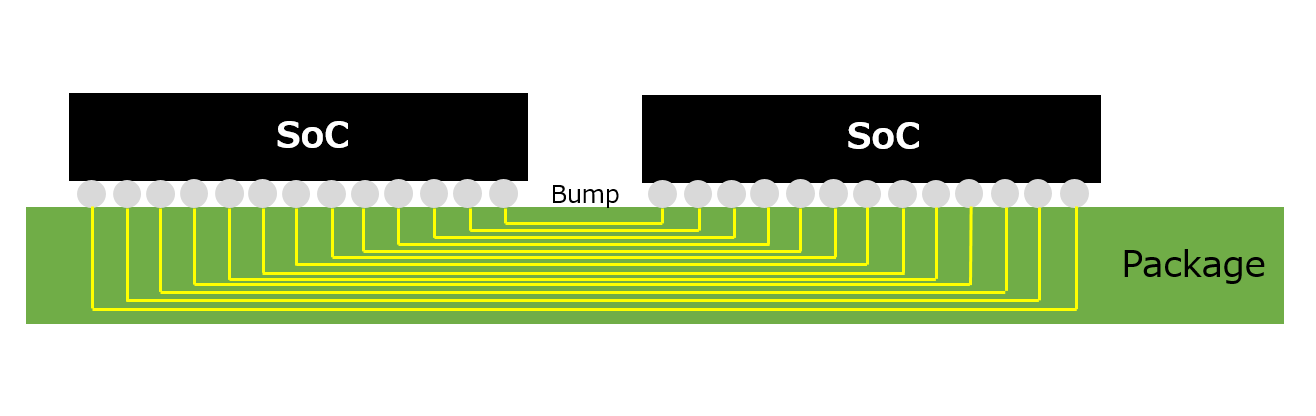

そこで、おさらいもかねてTSMCの3次元積層技術を解説しよう。まず下図が3次元積層「以前」である。インテルのCore 2 Duoなどがこの方式を採用している。AMDならEPYCやRyzen Threadripper、それと第3世代以降のRyzenがこれに該当する(Ryzen Gは含まず)。要するにパッケージ上に2つのSoCダイを搭載するための配線を埋め込み、これをBump(ハンダのボール)で接続する仕組みだ。これは通常3Dとは呼ばれない。

3次元積層以前の積層技術

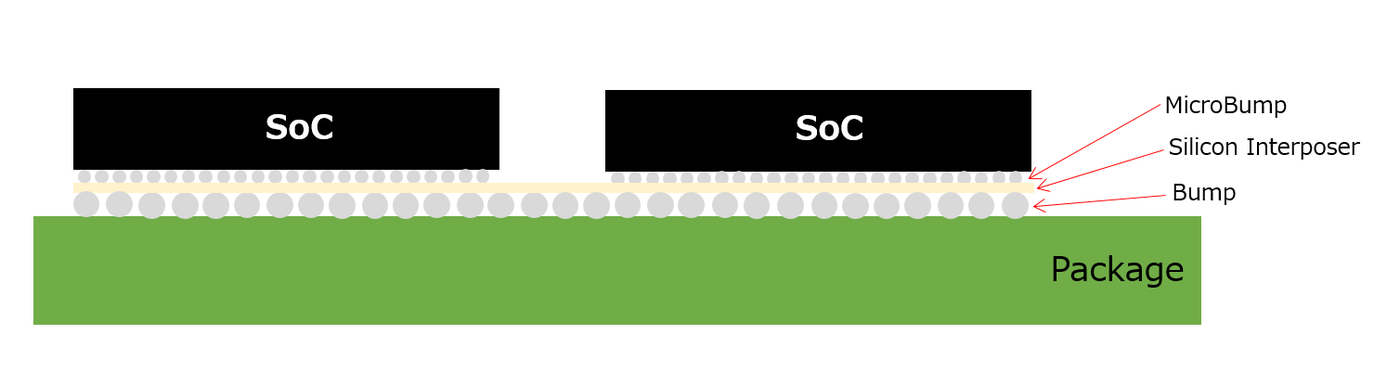

最初に3D(最近では2.5Dという呼び方が一般的)構成を取ったのは下図である。TSMCはこれをCoWoS(Chip on Wafer on Substrate)と呼んでいる。

最初の3次元積層技術となるCoWoS

CoWoSも最近は進化して、CoWoS-S/R/Lと目的別に多少進化しているが、基本的な構造は図のように、チップとパッケージの間にシリコン・インターポーザーを挟むことで、チップ間の配線を高速・高密度かつ低損失で可能にしたものだ。

ここでシリコン・インターポーザーと呼ぶのは、実際にこの間に挟まるインターポーザーは、LSIを作るのと同じ工程(=同じ材質)で製造されているからだ。CoWoSを最初に採用したのはFPGAメーカーのXilinxで、この時は28nmプロセスで製造されたFPGAのチップ同士を、TSMCの90nmプロセスで製造されたインターポーザー上に載せている。なお、この時はまだCoWoSという名前ではなかった。

これにより、FPGA同士の配線はパッケージを経由するときよりもはるかに短くなり、またパッケージ経由(配線間隔はがんばっても0.1mm単位)よりも高密度(必要なら100nm単位の間隔)での配線が可能になった。またパッケージ経由にすると配線損失も大きいため、1V以上(昔なら1.5~1.8V、今でも1~1.2V程度)の電圧で信号を駆動する必要があるが、インターポーザー経由だともっと低い0.4~0.6V程度での駆動が可能になるため、当然省電力につながる。

実際の利用例としてはHBM/HBM2メモリーの接続に使うケースが非常に多いが、これはHBM/HBM2は端子数が多すぎる(なにせあの小さなダイに3231個もの端子がある)から通常のパッケージでは接続できないためだ。ちなみにこのCoWoSに相当するインテルの技術がEMIB(Embedded Multi-die Interconnect Bridge)となる。