※この記事はASCII.jpからの転載です(文中リンクはASCII.jpの記事に飛ぶことがあります)

V-Cacheのおかげで歩留まりが改善し性能も向上する

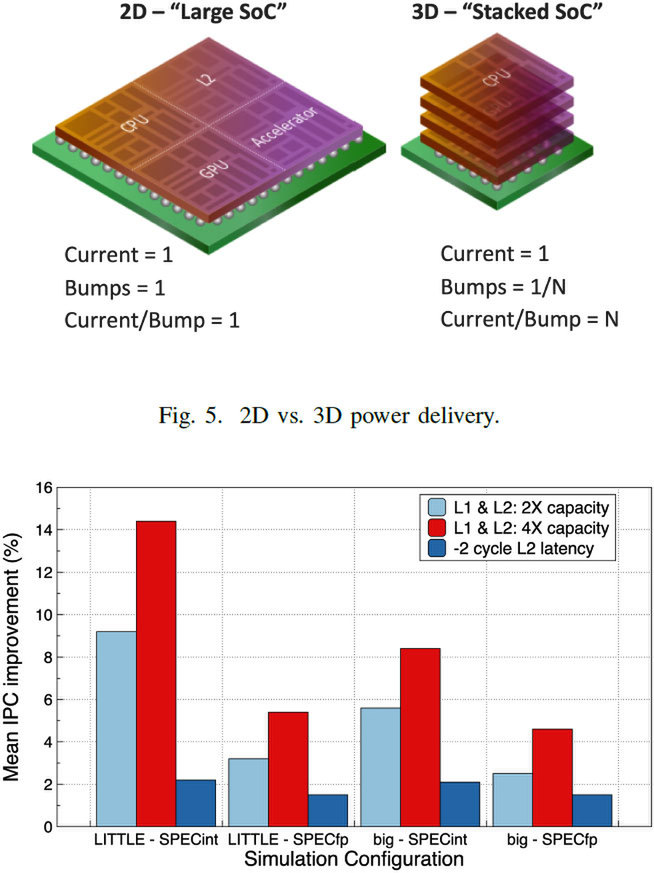

V-Cacheによるメリットは多い。まず最初は純粋に性能向上である。加藤勝明氏の記事にあるように、ゲームで平均15%のフレームレート向上があったとするが、実はこれ以外にもArmが2020年に出した“Stack up your chips: Betting on 3D integration to augment Moores Law scaling”という論文が興味深い。

これはArmのSoCを積層構成にして、その際に1次/2次キャッシュの容量を増やすとどう性能が変わるのかを論じたものだが、下の画像のグラフで示すように、bigコア/LITTLEコアや整数演算/浮動小数点演算で差があるものの、IPCが2~14%向上することが示されている。今回の場合は3次キャッシュなので直接この結果が適用できるわけではないが、わりとおもしろい結果である。

濃い青は「容量を変えずに2次キャッシュのレイテンシーを2サイクルに減らした場合の向上率」で、要するにレイテンシーを下げるより容量を増やした方が効果的というわけだ

2つ目は製品の歩留まりを改善できることだ。仮に同じ容量を積層技術を使わずに実現すると、CCDのサイズは150mm2を超えることになり、当然製品の歩留まりが落ちる。ところが3次元積層では、CCDとV-Cache×2を別々に製造しておき、まず不良品を撥ねて良品のみで積層できるため、結果的に歩留まりが大幅に上がることになる。少なくとも現在のZen 3よりも歩留まりが下がることはないのは大きなメリットだろう。

3つ目は製品ラインナップを増やす余地があることだ。先の話ではないが、V-Cacheなし(32MB L3)/1枚(64MB L3)/2枚(96MB L3)/4枚(160MB L3)といろいろバリエーションを用意できる。しかもそれを後工程で実現できるのは、製品展開の幅を広げることにつながる。

また今回はZen 3コア(最初のターゲットはEPYC向けだろう)だが、将来的には例えば次のRyzen G(コード名はRembrantらしい)や、その次(コード名はPhoenixだそうだ)の場合、L3兼インフィニティーキャッシュとして積層することで、大幅にGPU性能を引き上げ可能になるだろう。

あるいはNAVI系列についても、Radeon RX 6900 XTクラスはすでにインフィニティーキャッシュがやや不足気味で、特に4Kをフルにぶん回すとGeForce RTX 3090に追従しきれないシーンが見られたが、インフィニティーキャッシュにこれを応用して、例えば256MBなどに増量すればさらに性能が向上するだろう。

これまでダイサイズ肥大化を避けるためにギリギリで構成されていたキャッシュの容量を大幅に引き上げることで、絶対性能あるいは性能/消費電力比を引き上げるという新たな武器をAMDは手に入れたわけだ。