※この記事はASCII.jpからの転載です(文中リンクはASCII.jpの記事に飛ぶことがあります)

チップレットに3D積層を組み合わせた

新しいパッケージX3D

次がパッケージ技術で、今後は現在のチップレットに3D積層を組み合わせたX3Dという新しいパッケージを予定していることを明らかにした。

プロセッサー・チップレット(それがCPUかGPUかは別にして)は引き続き2.5Dのままで、DRAMだけ3D積層というハイブリッドを想定していると思われる

これは別にCPUに限った話ではない。現在のGPUの場合、連載515回で解説したDeffered Renderingの絡みがあるため、チップレット構成のGPUは作りにくい(*)という欠点があるが、GPGPU的な用途であればこうした使い方はあまり一般的ではないから、実はチップレット式にしやすい。

したがって、RDNAの将来製品は引き続き1ダイの構成が続くだろうが、後述するCDNAの将来製品はこのX3Dを使ったパッケージになっても不思議ではない。

あるいはHPC向けのEPYCなども、ローカルに大量のHBM2を4次キャッシュとして搭載することで、メモリー帯域の不足を補うといった使い方も可能になると思われる。

(*) Deferred Renderingでは、一番最後に各チップレットからフレーム全体への参照が発生する関係で、チップレット間の通信が非常に多くなって、ここがボトルネックになる

CPUとGPUの接続も

インフィニティー・ファブリックで相互接続になる

そのGPUであるが、Radeon Instinct向けのInfinityアーキテクチャーはさらに進化することも紹介された。

第2世代の場合、EPYC 1ソケットあたり4wayなので、2ソケットで8Wayということになる。ただこの場合それぞれの4枚同士はCPUを2つ(と、しかもPCIe Gen4)経由なので、かなり遅くなるのは致し方ない

初代EPYC、つまりNaplesプラットフォームでは4枚のRadeon InstinctをPCIe Gen3で接続する形態だった。

ところが第2世代EPYC、つまりRomeプラットフォームでは、CPUとRadeon Instinctの接続はPCIe Gen4になっただけだが、Radeon Instinct同士はインフィニティー・ファブリックで接続できることは連載485回で紹介した。

これが第3世代EPYCであるMilanプラットフォームでは、CPUとGPUの接続もインフィニティー・ファブリックになることが明らかにされた。

しかもインフィニティー・ファブリック同士が、昔のOpteronのように相互接続可能(これはイメージ図なので、実際はこうはならない可能性もあるが)ということで、大幅に性能が上がることが期待される。

余談だが、このMilanプラットフォームではRadeon InstinctがGPUカードの形をしていないのは、単にスペースが足りないからという可能性もあるが、そもそもインフィニティー・ファブリックを使うならPCIeカードである必要もないわけで、NVIDIAのTesla同様に独自のモジュールでの提供の可能性もありそうに思える。実装面積を抑えるためにも、なにも場所を取って冷却が面倒なPCIeカードを選ぶ必要はないからだ。

ちなみにMilanプラットフォームにおけるインフィニティー・ファブリックの帯域は、現在の2倍になることも明らかにされた。

まだPCIe Gen5は間に合わないのかもしれない。時期的には間に合っても不思議ではないし、実際はPCIe Gen5/インフィニティー・ファブリックの両対応の可能性もある

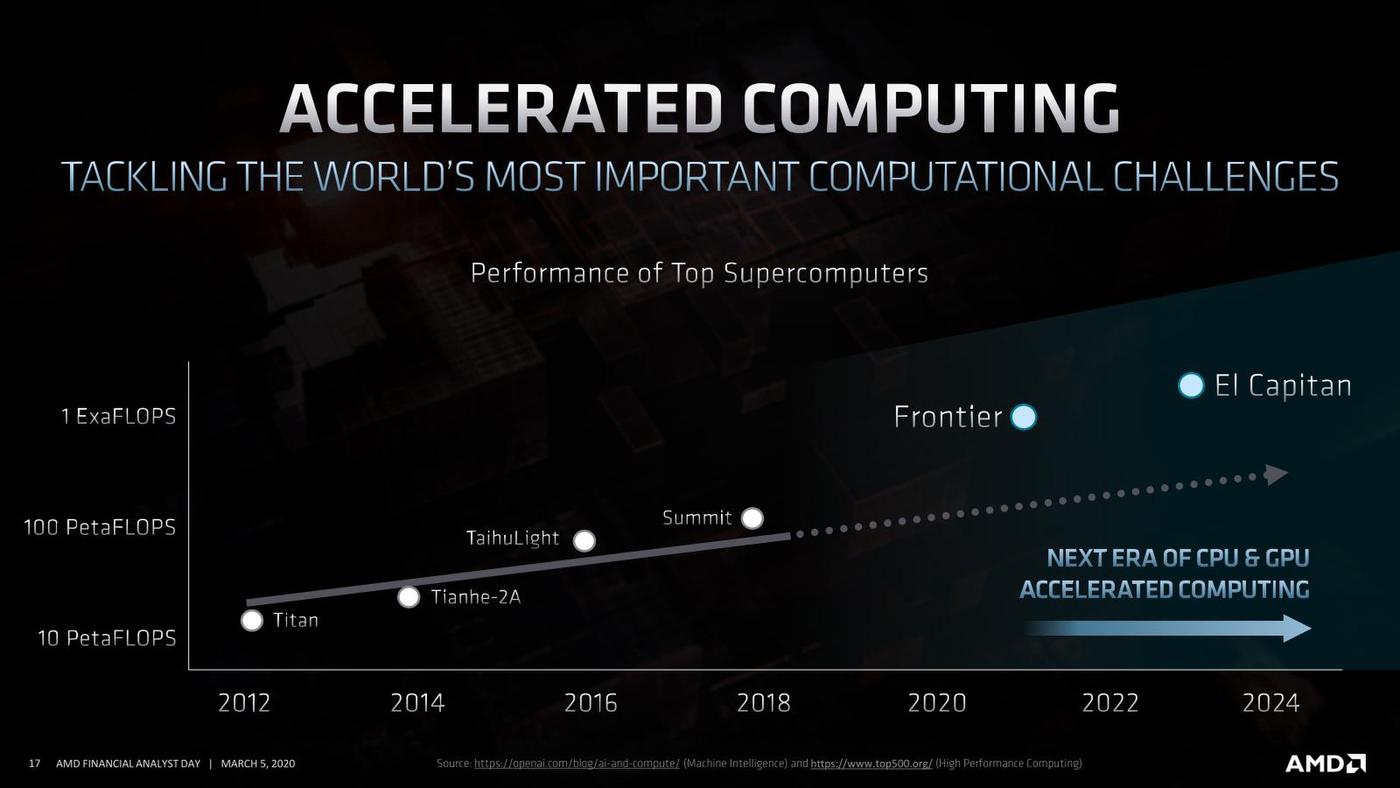

もう少し先の話をすると、2021年に納入されるスパコンFrontierに加え、2023年にはEl Captainという2 ExaFlopsのマシンをローレンス・リバモア国立研究所に納入することが3月4日に発表された。このEl Captainは次回詳しく解説しよう。

El CaptainはGenoa(Milanの次のZen 4ベースEPYC)が採用されるそうだ